קטגוריות: מעגלי מיקרו-בקר

מספר צפיות: 21445

הערות לכתבה: 0

מהי FPGA שפה פשוטה למתחילים

מה קשור לאלקטרוניקה דיגיטלית? קודם כל, עם אלמנטים לוגיים AND, OR, NOT. יתרה מזאת, רשימות משמרות, מפענחים, מכפילים וכו 'נכנסים לזיכרון. עם זאת, ככל שמורכבות המכשירים האלקטרוניים והמגמה לעבר מיניאטור גוברת, יצירת מכשירים המבוססים על מעגלים משולבים (IC) מהרכיבים לעיל הפכה קשה יותר, מכשירי IC המותאמים אישית של הטופולוגיה והמעגלים הנדרשים התבררו כדאיות רק כאשר המכשיר שוכפל במספרים גדולים, במקרים אחרים הוא היה יקר בצורה בלתי סבירה.

הדרך לצאת ממצב זה הייתה פיתוח מעגלי לוגיקה משולבים הניתנים לתכנות (קיצור FPGA, קיצור זר כמתקן לוגי הניתן לתכנות, PLD). מה זה ואיפה משתמשים בו נספר במאמר זה.

הבדלים מבקרי מיקרו

עם המילה "לתכנות", רוב המתחילים מקשרים עם מיקרו-בקרים. למרות העובדה שהם גם מתוכנתים, FPGA הם מכשיר שונה לחלוטין.

עבור מפתחים במיקרו-בקרים, קיימת מערכת קבועה של פתרונות ואמצעים הטמונים בשבב מסוים, היא לא תעבוד בשום דרך לסגת מהארכיטקטורה. ניתנת לך מערך של פקודות איתן אתה מבצע פעולות של אינטראקציה עם הסביבה, על ידי קריאת נתונים מכניסות דיגיטליות ואנלוגיות ושליחת אותות למפעילים באמצעות פלטים.

בנוסף, תוכלו לבצע חישובים, לשמור נתונים ברישומים או ב- ROM, כמו גם לפעול עם נתונים שהובקעו בזיכרון של בקר המיקרו. על זה, בעיקרו של דבר, המטרה והתכונות של עבודה עם בקרי מיקרו.

מעגלים משולבים לוגיים ניתנים לתכנות (FPGA) שונים זה מזה כשאתה מתכנת מכשיר, אתה עצמך יוצר ארכיטקטורה מאלמנטים לוגיים בסיסיים. לפיכך, אתה מקבל מהירות וגמישות גבוהה של השבב. זה מאפשר, בלי לשנות שבב אחד, לבצע מספר פרויקטים.

באופן כללי ניתן לחלק את מכשיר ה- FPGA הפנימי לשלוש קבוצות עיקריות:

1. מערך של אלמנטים לוגיים (תאים מאקרו, חסימות לוגיות).

2. חסימות קלט / פלט (IO).

3. קווי תקשורת בינם לבין המכשיר השולט בחיבורים אלה.

עם זאת, מבנה כזה הוא הכללי מאוד, נשקול נושא זה ביתר פירוט בהמשך.

על ידי תכנות, אתה מחבר את האלמנטים באותה צורה שאתה עושה, מרכיב מכשיר מאלמנטים בודדים ומחבר בין הכניסות והיציאות שלהם למוליכים.

הערה:

ההבדל העיקרי בין FPGA למיקרו-בקרים הוא שבמיקרו-בקר אינך יכול לשנות את החיבורים הפנימיים בין האלמנטים הפשוטים ביותר, והתכנות ועבודה איתם מבוסס על רישום חיבורים.

הבחירה במיקרו-בקרים מבוססת על קריטריונים רבים, כגון:

-

מהירות ומהירות שעון;

-

כמות ה- ROM וה- RAM;

-

מספר התשומות והתפוקות.

תכונות וציוד היקפיים נוספים פונקציונליים, כגון תמיכה בקווי תקשורת ופרוטוקולים (I2C, חוט אחד, אות PWM וכו ').

בעת בחירת FPGA, הקריטריון העיקרי הוא מספר הבלוקים הניתנים לתכנות - הם אמורים להספיק למשימה.

בהתאם ל- FPGA הספציפי, מספר החסימות יכול להשתנות באופן נרחב והעלות משתנה גם היא.

בקר המיקרו מבצע ברצף את כל הפעולות שנקבעו בתוכניתו, בעוד שחסימות FPGA מבצעות את המשימה במקביל ולא תלויות זו בזו, ולכן השוואה בין מכשירים אלה לפי תדר שעון אינה מעשית. עקרון הפעולה שלהם שונה מדי.

מינים

כרגע הם שני סוגים עיקריים של FPGAs:

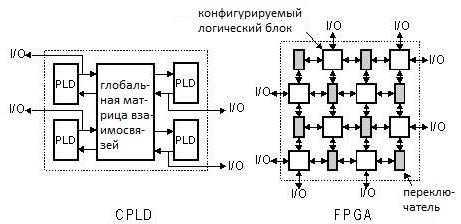

1. CPLD (התקן לוגי מורכב לתכנות - מעגל משולב לוגי לתכנות, למעשה, זהו FPGA במובנו הקלאסי). בדרך כלל יש לו זיכרון מובנה שאינו נדיף אליו נטענת הקושחה.

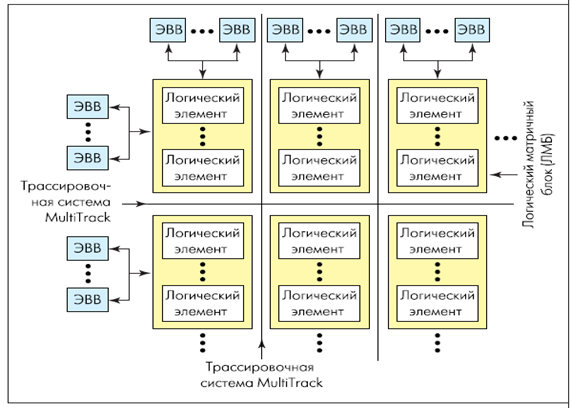

המבנה הפנימי בנוי על מטריצה של תאים מאקרו או בלוקים לוגיים, ומספר האלמנטים בהם נמצא בטווח של מאות ואלפי חלקים. בשל הפשטות היחסית שלהם, הם זולים יותר מהסוג הבא של היגיון לתכנות. כל זה מוביל לעובדה ש- CPLD משמש בעיקר במעגלים בהם יש צורך במהירות גבוהה ומספר גדול של תפוקות, תוך ביצוע משימות פשוטות.

2. FPGA (מערך שער הניתן לתכנות בשדה - מערך שער הניתן לתכנות על ידי משתמשים, עם זאת מכונה לעתים קרובות FPGA) - מכשירים מפותחים ומורכבים יותר בהשוואה ל- CPLD, בנויים על בלוקים לוגיים עם מיתוג גמיש ומכילים מספר גדול יותר של אלמנטים (עשרות או מאות אלפי חלקים).

קושחה בדרך כלל מאוחסנת בזיכרון חיצוני לא נדיף. בנוסף לאלמנטים ההיגיון הפשוטים ביותר, FPGAs יכולים להכיל בלוקים מוכנים לביצוע פעולות כלשהן, למשל בלוקים לעיבוד אותות DSP. כל זה מאפשר לכם ליישם מעבד, התקני עיבוד אותות והתקנים מורכבים אחרים.

מעניין:

למרות שלמעשה נוכחות של זיכרון לא נדיף אינה הופכת את CPLD לוגי לתכנות. זה מטעה חלקית. ההבדל העיקרי בין CPLD ו- FPGA הוא המבנה הפנימי.

התקן ה- CPLD הפנימי מוצג ביתר פירוט באיור למטה.

והתכנית המשוערת של המאקרובל שלה נראית כך:

המאקרו סל מורכב ממכפילים רב-תכניים שניתן לתכנות, מפעילים (אחד או יותר) ויוצר קבוצה של אותות FB פלטים במספר גרסאות.

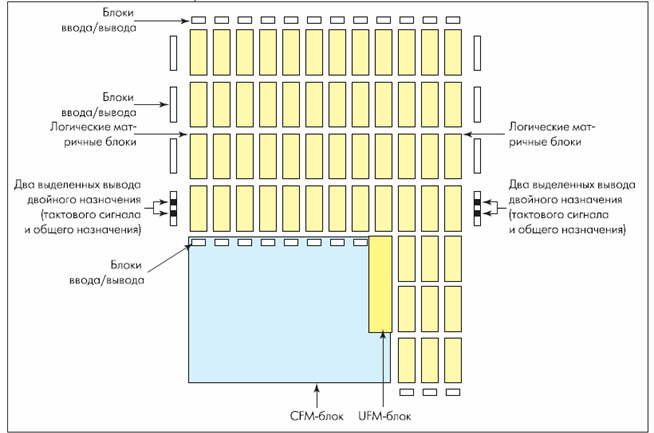

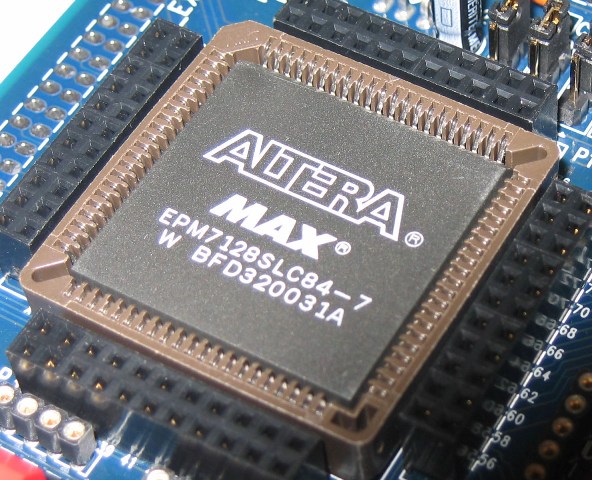

להלן דוגמא נוספת - תרשים חסימה של שבב CPLD ממשפחת השבבים של Altera MAX II.

והתכנית המבנית של השבבים של אותה משפחה.

צמיגי ביניים מוקצים לתאי מאקרו באמצעות צומת כמו מפיץ באנגלית. זה נשמע כמו Allocator Logic, שמוצג בתרשים למטה, הוא מראה גם את מטריצת המיתוג (Global Routing Pool), ובתאי המאקרו (תאי מאקרו) יש שני פידבקים.

היציאות החיצוניות של המעגל המיקרו מחוברות לפלטים של תאי המאקרו דרך בלוק אחר (מטריקס) - ORP (פלט ניתוב פלט), שימו לב שדרכו לוגיקת ה- INPUT מחוברת ל- GRP, כפי שמוצג באיור שלהלן.

הערה:

לחלק מה- CPLDs יש מה שנקרא כניסות ישירות (קלט ישיר) - הן מחוברות לכניסות התאים באופן ישיר, מה שמקטין עיכובים.

למבנה ה- FPGA יש את הצורה:

-

L - בלוק הניתן להגדרה הגיונית;

-

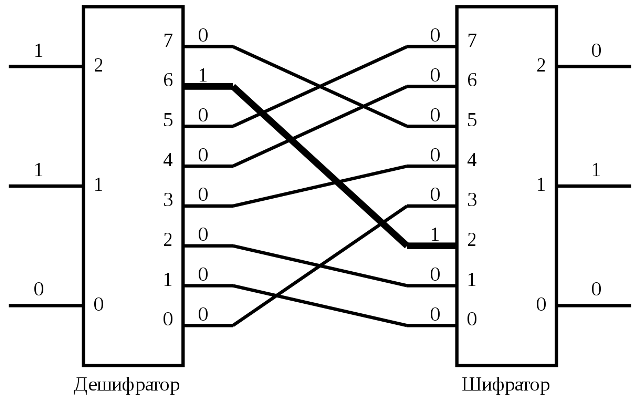

S (בלוק החלפה) - בלוק החלפה, הוא מקבל מספר מסוים של ביטים לכל תנועה, ממיר, לפי אלגוריתם מסוים, ומוצא מספר שונה של ביטים בפלט. במילים אחרות, מפענח, מקודד ומתג.

-

C (חסימת חיבור) - חסימת חיבור.

תרשים חסימת S:

תכנות

HDL (שפת תיאור חומרה) - זו השפה שבה מתוכנתים FPGAים. פופולרי ורב תכליתי הם Verilog HDL ו- VHDL. קיימות שפות אחרות, כמו אלה הספציפיות ליצרנים, כמו AHDL למוצרי ALTERA.

תכנות גרפית זמינה למפתחים העובדים עם FPGAs. כלומר, תוכלו פשוט לצייר מעגלי לוגיקה או לשלב קוד עם גרפיקה. האחרון נקרא שיטת הפיתוח המודולרי, כאשר נקבעים מודולים ספציפיים, והמודול העליון, בו משולב הכל, מתוכנת בצורה גרפית.

דוגמאות ליצרנים וסדרות פופולריות

בזמן הכתיבה המפורסמים ביותר הם המוצרים של שני יצרנים.

-

אלתרה (נוסדה בשנת 1983);

-

קסילינקס (נוסדה בשנת 1984).

לאלטרה יש כמה סדרות עיקריות של היגיון לתכנות:

-

MAX, MAX II, MAX IIZ;

-

7000S;

-

3000A;

-

מקס V;

-

ציקלון

-

אריה;

-

סטרטיקס

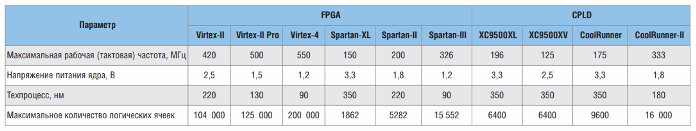

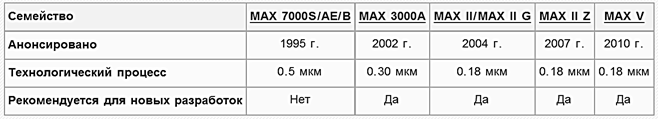

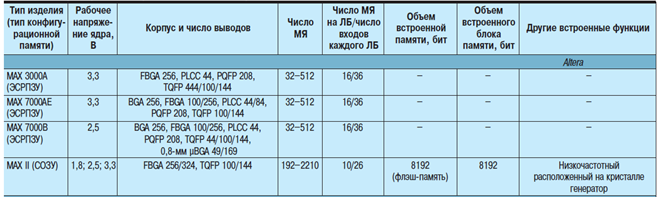

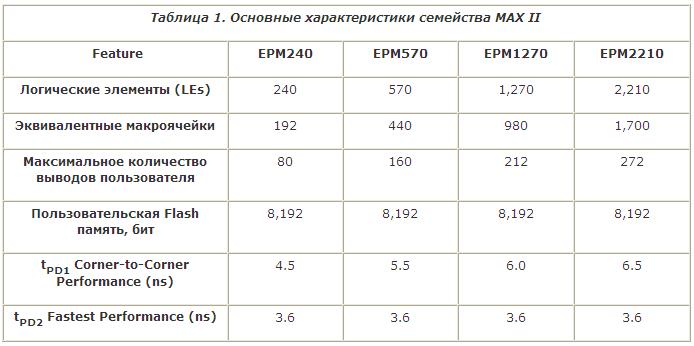

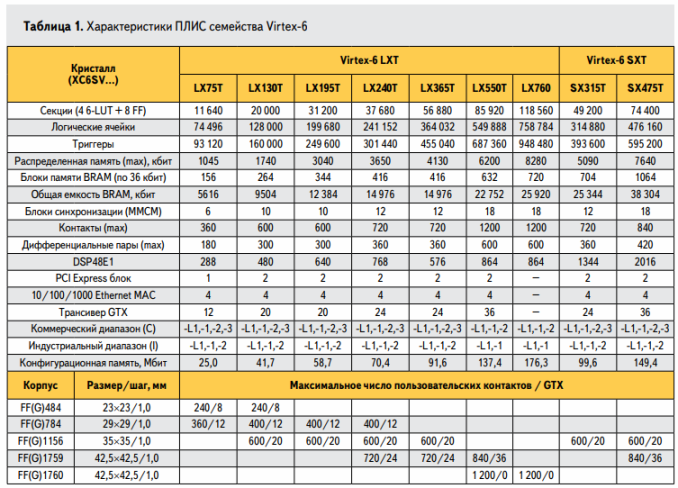

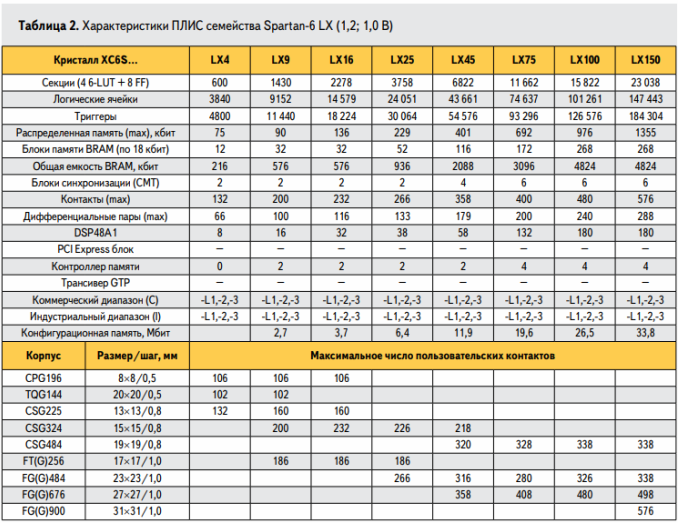

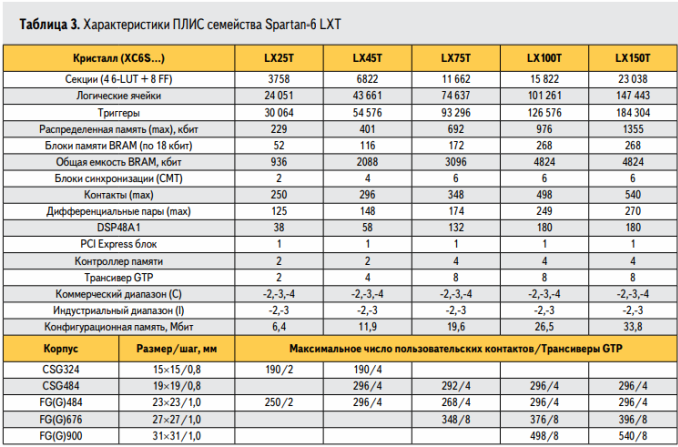

בואו נתייחס לכל אחד מהם ביתר פירוט. בטבלאות שלהלן אתה רואה מידע כללי על שבבי המשפחה.

אלתרנה 3 CPLD CPLD:

-

MAX הוא CPLD לשימוש במכשירים ניידים, סימני ההיכר הם צריכת חשמל נמוכה יחסית ופיזור חום. בהתאם למורכבות ושנות השחרור, נבדלים השינויים הבאים:

-

7000S מיושנת עד כה, היא שוחררה בשנת 1995.

-

3000A - יצא בשנת 2002, מיוצר בטכנולוגיית 300nm. מורכב ממספר קטן של תאי מאקרו (32-512)

-

MAX II שיצא בשנת 2004 מיוצר בטכנולוגיית 100 ננומטר, מורכב ממספר גדול יותר של יחידות (240-2210) הפועלות בתדרים של עד 304 מגהרץ. המוצר מיוצר במקרים מסוג TQFP 0.5 מיל עם 100 רגליים ומעלה.

-

MAX IIZ - 2007, התכונה העיקרית היא צריכת חשמל מופחתת - זו נקודה חיובית, עם זאת, התדרים מופחתים ל 152 מגה הרץ. מעגלי מיקרו אלה מופעלים מ- 1.8 V.

-

MAX V - שנת 2010. הוא מיוצר על פי טכנולוגית 180 ננומטר, הוא יכול להכיל בין 40 ל 2210 בלוקים ופועל בתדרים עד 152 מגה הרץ או 304 מגה הרץ - זה תלוי במספר הבלוקים.

FPGA:

-

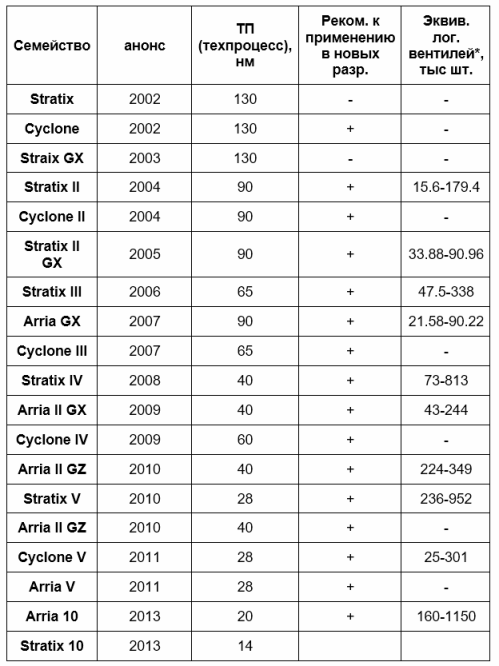

ציקלון הוא שבב מסוג FPGA תקציב. ישנם חמישה דורות שמסומנים במספרים יווניים (מ- I עד V בהתאמה). הדור הראשון הושק בשנת 2002, הופק בטכנולוגיית 180 ננומטר, והדור החמישי שוחרר בשנת 2011 ויוצר בטכנולוגיית 28 ננומטר. ראוי לציין שכל הדורות נשארים רלוונטיים.

-

Arria - מתייחסים גם ל- FPGA הבינוני.

-

Stratix - FPGAs עוצמתיים.

להלן טבלאות ציר ההיגיון לתכנות של Altera FPGA.

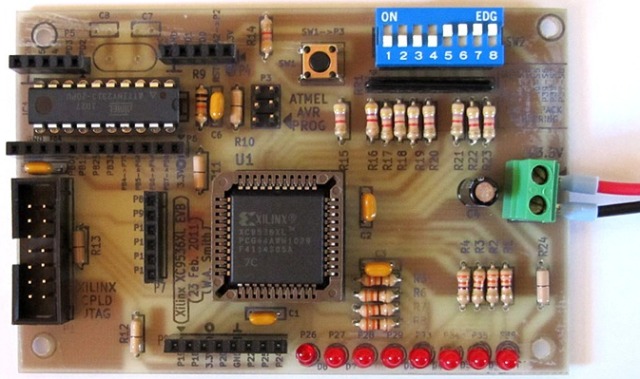

היצרן Xilinx CPLD שהוצג בסדרה:

-

XC9500XL של 36-288 תאי מאקרו. הם פועלים בתדרים של עד 178 מגה הרץ, ומודלים במהירות 288 תאים מאקרו במהירות של 208 מגה הרץ. זה מתבצע כמו במקרים קטנים עם 44 סיכות (מובילים) במרחק של 0.8 מ"מ זה מזה - מקרים כאלה נחשבים למלחמים בקלות. ניתן להשיג גם עם 64 ו 100 רגליים במרווחים של 0.5 מ"מ, כמו גם דגמים במארזים מסוג PLCC.

-

סדרת CoolRunner-II היא CPLD חסכוני באנרגיה ועתיד פרודוקטיבי. תכונה מופעלת על ידי מתח של 1.8 וולט, הכניסות והיציאות מיועדים לפעול בטווח של 1.5-3.3V. הם מורכבים מ- 32-512 תאים מאקרו ומיוצרים בטכנולוגיית 180 ננומטר. תלוי במספר התאים, הם עובדים בטווח התדרים 179-323 מגהרץ, וככל שהתאים קטנים יותר, כך הם יכולים לעבוד בתדירות גבוהה יותר במקרה זה. הם נמצאים במקרים שונים, כולל מולחמים בקלות, כמו במעגלי המיקרו של הסדרה הנחשבים לעיל.

חברת קסילינקס לא עברה במקום ו- FPGA:

-

Spartan-6 - מורכב מגושי כניסה של 6 קלט, המספר שלהם נע בטווח של 3840-147443 חלקים. מעניין בכך שהם עשויים להכיל בקרים להחלפת נתונים כמו DDR2, DDR3, PCI-EXPRESS, Ethernet 1Gbit, SerialATA וכו '...

-

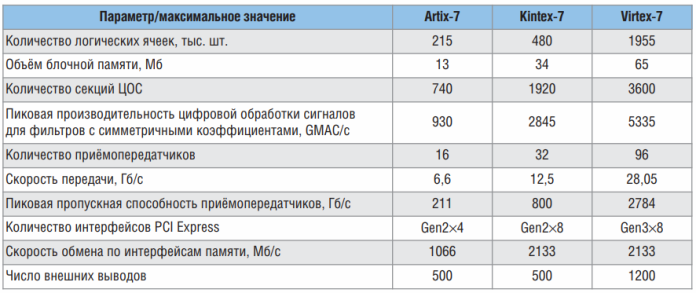

סדרת Vitrex-7 מורכבת, מעגלי מיקרו יכולים להכיל עד 2,000,000 בלוקים לוגיים ו -1,200 אנשי קשר.

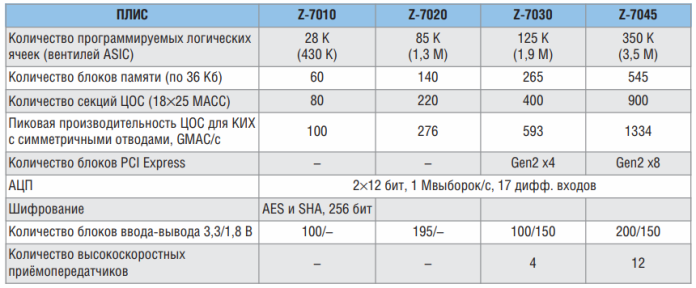

להלן תוכלו למצוא את טבלאות הסיכום עם מפרטי CPLD ו- FPGA מסדרת Xilinx 6 ו- 7, כמו גם Zynq-7000.

מסקנה

FPGAs ו- PPVM מיוצרים גם על ידי חברות אחרות כמו Lattice Semiconductor (בשנת 2002 החלו לייצר FPGA), Actel, והקוראים הידועים באתר שלנו. בקרי מיקרו ורבים אחרים. בלוגיקה הניתנת לתכנות תוכלו ליישם מספר מכשירים, ליישם חישובים מקבילים שאינם תלויים זה בזה במכשיר אחד, עם זאת, עבור פרויקטים ביתיים, רכישתם לעתים קרובות אינה מוצדקת כלכלית, אך יחד עם זאת סבירה למדי בסולם ייצור, כחלופה למעגלים משולבים בהתאמה אישית.

P.S.צפו בסרטון, בו תוכלו לראות דוגמא ליישום קונסולת המשחקים של נינטנדו ב- FPGA:

ראה גם באתר elektrohomepro.com

: